这些铜缆,蓝链或OPA都不能在最大信号速率下运行超过3米或10英尺。它以3米物理跨距将链接着CPU和TPU2板的互连拓扑结合在一起。Google使用彩色电缆;而我的猜测是,这使组装更容易,而且没有布线错误。请参见上图中最前面连接器下方的电缆颜色的贴纸。我们认为,颜色编码是Google计划大规模部署这些TPU2机柜的标志。

白色电缆最有可能是1 Gb /秒以太网系统管理网络。我们没有看到Google可以将管理网络连接到照片中的TPU2板。但是,基于白色电缆的路由,我们可以假设Google将管理网络从后端连接到处理器板。也许处理器板通过OPA连接管理和评估TPU2板的健康状况。

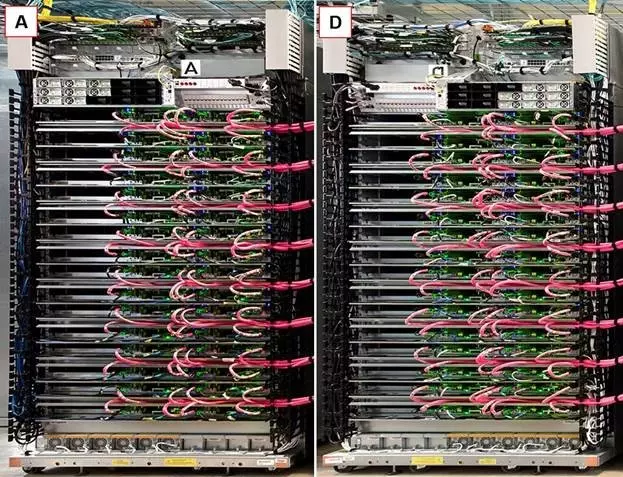

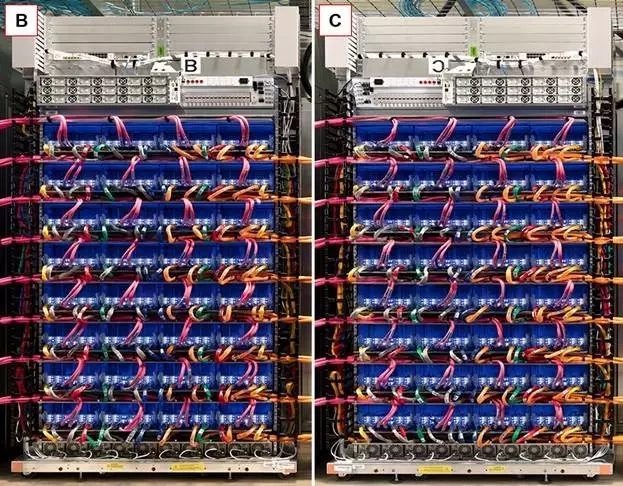

Google的TPU2机架机柜具有双边对称性。在下图中,我们翻转了处理器机架D以将其与处理器机架A进行比较。这两个机架是相同但相互镜像的图像。之后的图,很明显,机架B和C也是彼此的镜像。

将两个CPU机架与机架D进行比较

将两个CPU机架与机架C进行比较

Google的照片中没有足够的可见的连线来确定确切的互连拓扑,但它看起来像是一种超网格互连。

我们相信,CPU板是标配英特尔至强双socket主板,适合Google的1.5英寸服务器外形尺寸。它们是当前一代主板设计,考虑到它们有OPA,它们可能是Skylake板(参见下面的功耗讨论)。我们相信它们是双socket主板,仅仅是因为我还没有听说过许多单socket主板是通过英特尔供应链的任何一部分发货的。但是随着新市场进入者,如具有“Naples”Epyc X86服务器芯片的AMD,和具有Centriq ARM服务器芯片的Qualcomm强调单socket配置,这种情况可能会有所改变。

我们认为Google将每个CPU板连接到一个TPU2板上,使用两条OPA电缆实现了25 GB / s的总带宽。这种一对一的连接解决了TPU2的一个关键问题――Google以TPU2芯片与Xeon插座的比例为2:1的方式设计了TPU2 stamp。也就是说,每个双插槽Xeon服务器都有四个TPU2芯片。

TPU2加速器与处理器的这种紧密耦合与深度学习训练任务中GPU加速器的4:1至6:1的典型比例大不相同。低2:1的比例表明,Google保留了原始TPU中使用的设计理念:“与GPU相比,TPU在理念上更接近于FPU(浮点单元)协处理器。”处理器在Google的TPU2架构中仍然有很多工作要完成,但它正在将所有的矩阵数学卸载到TPU2上去。

我们看不到TPU2 机柜中的任何存储。大概这是在下图中大束蓝色光缆所追踪的那样。数据中心网络连接到CPU板,但是并没有光纤电缆连接到机架B和C上,同样,TPU2板上没有网络连接。

许多光纤带宽连接到Google数据中心的其余部分

每个机架有32个计算单位,无论是TPU2还是CPU都是如此。因此,每个机柜中有64个CPU板和64个TPU板,共有128个CPU芯片和256个TPU2芯片。

谷歌表示,其TRC包含1000个TPU2芯片,但是这一数字略有下降。四个机柜包含1024个TPU2芯片。因此,四个机柜是Google已经部署了了的TPU2芯片数量的下限。从Google I / O大会期间发布的照片中可以看到三个(业可能是四个)机柜。

不清楚处理器和TPU2芯片是如何通过一个机柜进行联合,以便TPU2芯片可以在超网格中跨链接有效地共享数据的。但我们几乎可以肯定,TRC不能跨越四个机柜(256个TPU2芯片)中的一个以上的单个任务。原始TPU是一个简单的协处理器,因此处理器处理所有数据流量。在这种架构中,处理器通过数据中心网络从远程存储器访问数据。

关于机柜模型也没有很多的描述。 TPU2芯片可以在OPA上使用远程直接存储器访问(RDMA)从处理器板上的内存中加载自己的数据吗?这好像是可以的。处理器板似乎也可能在机柜上执行相同操作,创建大型共享内存池。该共享内存池不会像Hewlett Packard Enterprise的机器共享内存系统原型中的内存池那么快,但是使用25 GB / s的链接,它的速度也不会太慢,内存依旧很大,这是在两位tb范围内的(每个DIMM 16 GB,每个处理器有8个DIMM,每个板有两个处理器,64个板产生16 TB的内存)。

我们推测,在一个机柜上安排一个需要多个TPU2的任务看起来像这样:

处理器池应该有一个机柜的超网格拓扑图,哪些TPU2芯片可用于运行任务。

处理器组可能联合编程每个TPU2以明确地连接位于两个相连接的TPU2芯片之间的网格。

每个处理器板将数据和指令加载到其配对的TPU2板上的四个TPU2芯片上,包括网状互连的流量控制。

处理器在互连的TPU2芯片之间同步引导任务。

当任务完成时,处理器从TPU2芯片收集所得到的数据(该数据可能已经通过RDMA存储在全局存储器池中),并将TPU2芯片标记为可用于另一任务。

这种方法的优点是TPU2芯片不需要理解多任务,虚拟化或多租户――处理器的任务是处理所有跨越机柜的这些任务。

这也意味着如果Google曾经提供Cloud TPU实例作为其Google Cloud Platform自定义机器类型IaaS的一部分,该实例将必须包括处理器和TPU2芯片。

还不清楚的是,工作负载能否可以跨stamp进行缩放,并保留超级网格的低延迟和高吞吐量。虽然研究人员可能可以通过TRC访问1,024个TPU2芯片中的一些,但跨stamp进行扩展工作负载看起来仍是一个挑战。研究人员可能有能力连接多达256个TPU2芯片的集群,这足以令人印象深刻,因为云GPU连接目前正在扩展到32个互连设备(通过Microsoft的Olympus HGX-1设计)。

Google的第一代TPU在负载下消耗40瓦特,同时以23 TOPS的速率执行16位整数矩阵乘法。Google将TPU2的运行速度提高到45 TFLOPS,同时通过升级到16位浮点运算来提高计算复杂度。根据一个粗略的经验法则来看的话,这至少是两倍的功耗――如果除了将速度提高两倍以及转移到FP16外,什么也不做的话,TPU2必须消耗至少160瓦。散热器尺寸显示出更高的功耗,某处甚至高于200瓦特。

转载请注明出处。

相关文章

相关文章 精彩导读

精彩导读 热门资讯

热门资讯 关注我们

关注我们