从Google的TPU2横空出世后,我们还差一个用途详解(3)

2017-05-24 编辑:

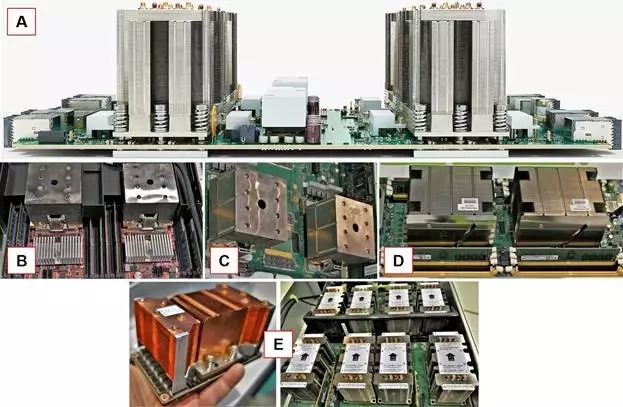

TPU2板具有位于TPU2芯片顶部的巨大散热片。它们是多年来我看到的最高的风冷散热片。它们具有内部密封环液体循环。在下图中,我们将TPU2散热片与过去几个月看到的最大的可比散热片进行相比较。

散热片遍历:A是四路TPU2主板侧面视图,B为双IBM Power9“Zaius”主板,C为双IBM Power8“明斯基”主板,D为双英特尔至强Facebook“优胜美地”主板,E为Nvidia P100 SMX2 模块与散热片和Facebook“Big Basin”主板

这些散热器的尺寸大多“每个超过200W”。很容易看出,它们比原始TPU上的40瓦散热器大得多。这些散热器填补了两个Google垂直的1.5英寸,Google外形尺寸单元空缺,因此它们几乎高达三英寸。(Google机架单元高度为1.5英寸,比行业标准1.75英寸U型高型号矮一点)。

这是一个很好的选择,每个TPU2芯片还有更多的内存,这有助于提高吞吐量并增加功耗。

此外,Google从单芯片TPU芯片(PCI-Express插槽向TPU卡供电)转移到单芯片TPU2板设计共享双OPA端口和交换机,以及为每个TPU2芯片提供两个专用的BlueLink端口。 OPA和BlueLink都增加了TPU2板级功耗。

Google的开放计算项目机架规格设备显示6千瓦,12千瓦和20千瓦的电力输送配置文件; 20千瓦的功率分配可以实现90瓦的CPU处理器插座。我们猜测,使用Skylake一代Xeon处理器和处理大部分计算负载的TPU2芯片,机架A和D可能使用20千瓦电源。

而机架B和C就是另一个不同的故事了。功率输送为30千瓦,能够为每个TPU2插座提供200瓦的功率输送;每个机架36千瓦将为每个TPU2插座提供250瓦的功率输送。36千瓦是一种常见的高性能计算能力传输规范。我们认为,每芯片250瓦功耗也是Google愿意为上述巨大的TPU2散热器支付的唯一原因。因此,单个TPU2 机柜的功率传输可能在100千瓦至112千瓦范围内,并且可能更接近较高数量。

这意味着TRC在满负荷运行时消耗将近一百兆瓦的功率。虽然四枚邮票部署成本昂贵,但却是一次性的资本费用,并不占用大量的数据中心空间。然而,半数兆瓦的电力是大量经营费用,持续资助学术研究,即使是一家Google规模的公司。如果TRC在一年内仍然运行,这表明Google正在认真研究其TPU2的新用例。

TPU2 机柜包含256个TPU2芯片。每个TPU2芯片的性能为45 teraflops,每个stamp产生总共11.5 petaflops的深度学习加速器的性能。这是令人印象深刻的,即使它确实是FP16的高峰表现。深度学习训练通常需要更高的精度,因此FP32矩阵乘法性能可能是FP16性能的四分之一,或者每个机柜约为2.9 petaflop,整个TRC为11.5 FP32 petaflops。

在峰值性能方面,这意味着在整个机柜上的FP16操作(不包括CPU性能贡献或位于机柜之外的存储),每千瓦跳跃到115吉比特每千瓦。

英特尔公布了双插槽Skylake生成Xeon核心计数和功耗配置后,可以计算Xeon处理器的FP16和FP32性能,并将其增加到每瓦特的总体性能。

关于Google的TPU2机柜行为还没有足够可靠的信息将其与像Nvidia的“Volta”这样的新一代商业加速器产品进行比较。架构的差别太大了,无需对同一任务中的两个架构进行基准测试。比较峰值FP16的性能就像将两台具有不同处理器,存储器和基于处理器频率的图形选项的PC的性能进行比较。

也就是说,我们认为真正的比赛不在芯片级别。挑战是将计算加速器扩展到普通比例。NVIDIA公司正在采用NVLink的第一步,从处理器上获得更大的加速器独立性。Nvidia正在将其软件基础架构和工作负载从单一GPU扩展到GPU集群。

Google选择将其原始TPU扩展为直接链接到处理器的协处理器。TPU2还可以进行扩展,作为以直接2:1比例的加速器进行处理任务。然而,TPU2超网格编程模型似乎没有可以将扩展任务做得很好的工作负载。但是,Google正在寻找第三方帮助来查找使用TPU2架构扩展的工作负载。

相关阅读:

相关推荐: